# HT9200A/B DTMF Generators

#### Features

- Operating voltage: 2.0V~5.5V

- Serial mode for the HT9200A

- Serial/parallel mode for the HT9200B

- Low standby current

## **General Description**

The HT9200A/B tone generators are designed for  $\mu$ C interfaces. They can be instructed by a  $\mu$ C to generate 16 dual tones and 8 single tones from the DTMF pin. The HT9200A provides a serial mode whereas the HT9200B contains a

- Low total harmonic distortion

- 3.58MHz crystal or ceramic resonator

- HT9200A: 8-pin DIP/SOP package HT9200B: 14-pin SOP package

selectable serial/parallel mode interface for various applications such as security systems, home automation, remote control through telephone lines, communication systems, etc.

#### **Selection Table**

| Function<br>Part No. | Operating<br>Voltage   | OSC<br>Frequency    | Interface       | Package   |

|----------------------|------------------------|---------------------|-----------------|-----------|

| HT9200A              | $2V \sim 5.5V$         | $3.58 \mathrm{MHz}$ | Serial          | 8 DIP/SOP |

| HT9200B              | <b>HT9200B</b> 2V~5.5V |                     | Serial/Parallel | 14 SOP    |

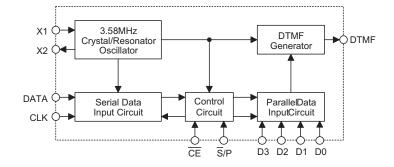

#### **Block Diagram**

1

## **Pin Assignment**

| CE                     | 1 | 8 | □ VDD  |  |

|------------------------|---|---|--------|--|

| X2                     | 2 | 7 | □ DTMF |  |

| X1                     | 3 | 6 | □ DATA |  |

| VSS                    | 4 | 5 | □ CLK  |  |

| HT9200A<br>- 8 DIP/SOP |   |   |        |  |

# Pad Assignment

| Р          | ad Coo  |         | Unit: µm   |         |         |

|------------|---------|---------|------------|---------|---------|

| Pad<br>No. | X       | Y       | Pad<br>No. | X       | Y       |

| 1          | -553.30 | 430.40  | 8          | 553.30  | -523.50 |

| 2          | -553.30 | -133.50 | 9          | 553.30  | -190.30 |

| 3          | -553.30 | -328.50 | 10         | 553.30  | 4.70    |

| 4          | -553.30 | -523.50 | 11         | 553.30  | 340.30  |

| 5          | -220.10 | -523.50 | 12         | 374.90  | 523.50  |

| 6          | -25.10  | -523.50 | 13         | -279.30 | 523.50  |

| 7          | 308.10  | -523.50 |            |         |         |

HT9200B - 14 SOP

$14 \cup VDD$   $13 \cup DTMF$   $12 \cup DATA$   $11 \cup CLK$   $10 \cup \overline{S}/P$   $9 \cup D3$   $8 \cup D2$

X2 🗆 2 X1 □ 3 VSS □ 4 NC 5 D0 🗆 6 D1 🛛 7

Chip size:  $1460 \times 1470 \; (\mu m)^2$

$\ast$  The IC substrate should be connected to VSS in the PCB layout artwork.

#### **Pin Description**

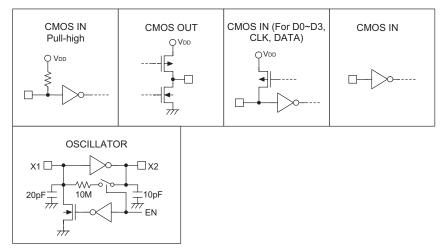

| Pin Name | I/O | Internal<br>Connection | Description                                                                                                                                                   |

|----------|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE       | Ι   | CMOS IN<br>Pull-high   | Chip enable, active low                                                                                                                                       |

| X2       | 0   |                        | The system oscillator consists of an inverter, a bias resistor, and                                                                                           |

| X1       | Ι   | Oscillator             | the required load capacitor on chip.<br>The oscillator function can be implemented by Connect a stan-<br>dard 3.579545MHz crystal to the X1 and X2 terminals. |

| VSS      | _   |                        | Negative power suppl, ground                                                                                                                                  |

| NC       |     |                        | No connection                                                                                                                                                 |

February 13, 2001

$\mathbf{2}$

| Pin Name | I/O | Internal<br>Connection              | Description                                                                                                                                                                                                                                        |

|----------|-----|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0~D3    | Ι   | CMOS IN<br>Pull-high<br>or Floating | Data inputs for the parallel mode<br>When the IC is operating in the serial mode, the data input ter-<br>minals (D0~D3) are included with a pull-high resistor. When<br>the IC is operating in the parallel mode, these pins become<br>floating.   |

| Ī/P      | Ι   | CMOS IN                             | Operation mode selection input<br>S/P="H": Parallel mode<br>S/P="L": Serial mode                                                                                                                                                                   |

| CLK      | Ι   | CMOS IN<br>Pull-high<br>or Floating | Data synchronous clock input for the serial mode<br>When the IC is operating in the parallel mode, the input termi-<br>nal (CLK) is included with a pull-high resistor. When the IC is<br>operating in the serial mode, this pin becomes floating. |

| DATA     | Ι   | CMOS IN<br>Pull-high<br>or Floating | Data input terminal for the serial mode<br>When the IC is operating in the parallel mode, the input termi-<br>nal (DATA) is included with a pull-high resistor. When the IC is<br>operating in the serial mode, this pin becomes floating.         |

| DTMF     | 0   | CMOS OUT                            | Output terminal of the DTMF signal                                                                                                                                                                                                                 |

| VDD      | _   |                                     | Positive power supply, 2.0V~5.5V for normal operation                                                                                                                                                                                              |

#### Approximate internal connection circuits

3

## **Absolute Maximum Ratings**

| Supply Voltage0.3V to 6V               | Storage Temperature– $50^{\circ}$ C to $125^{\circ}$ C  |

|----------------------------------------|---------------------------------------------------------|

| Input VoltageV_{SS}–0.3 to V_{DD}+0.3V | Operating Temperature– $20^{\circ}$ C to $75^{\circ}$ C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

#### **Electrical Characteristics**

Ta=25°C

| Sh al                      | Parameter                                                 |                 | Test Conditions                                                                 | Min.                  | <b>T</b>           | Ман                    | Unit |

|----------------------------|-----------------------------------------------------------|-----------------|---------------------------------------------------------------------------------|-----------------------|--------------------|------------------------|------|

| Symbol                     | Parameter                                                 | V <sub>DD</sub> | Conditions                                                                      | wiin.                 | Тур.               | Max.                   |      |

| V <sub>DD</sub>            | Operating Voltage                                         |                 |                                                                                 | 2                     |                    | 5.5                    | V    |

| I <sub>DD</sub>            | Operating Current                                         | 2.5V            | $\underline{-}$                                                                 |                       | 240                | 2500                   | μA   |

| -00                        |                                                           | 5.0V            | CE=V <sub>SS</sub> , No load                                                    |                       | 950                | 3000                   | μ    |

| $V_{IL}$                   | "Low" Input Voltage                                       |                 |                                                                                 | VSS                   |                    | $0.2V_{DD}$            | V    |

| $\mathrm{V}_{\mathrm{IH}}$ | "High" Input Voltage                                      |                 |                                                                                 | $0.8 \mathrm{V_{DD}}$ |                    | V <sub>DD</sub>        | V    |

| I <sub>STB</sub>           | Standby Current                                           | 2.5V            | $\overline{S}/P=V_{DD},\overline{CE}=V_{DD},$                                   |                       |                    | 1                      |      |

| <sup>1</sup> STB           | Stanuby Current                                           | 5.0V            | No load                                                                         |                       |                    | 2                      | μA   |

| $R_P$                      | Dull high Pagistance                                      | 2.5V            | V <sub>OL</sub> =0V                                                             | 120                   | 180                | 270                    | kΩ   |

| ць                         | Pull-high Resistance                                      | 5.0V            | VOL-0V                                                                          | 45                    | 68                 | 100                    | K75  |

| $t_{\mathrm{DE}}$          | DTMF Output Delay<br>Time (Parallel Mode)                 | 5V              |                                                                                 |                       | t <sub>UP</sub> +6 | t <sub>UP</sub> +8     | ms   |

| V <sub>TDC</sub>           | DTMF Output DC<br>Level                                   | 2V~<br>5.5V     | DTMF Output                                                                     | $0.45 V_{DD}$         |                    | $0.75 \mathrm{V_{DD}}$ | v    |

| I <sub>TOL</sub>           | DTMF Sink Current                                         | 2.5V            | $V_{DTMF}=0.5V$                                                                 | -0.1                  |                    |                        | mA   |

| V <sub>TAC</sub>           | DTMF Output AC<br>Level                                   | 2.5V            | Row group, $R_L=5k\Omega$                                                       | 0.12                  | 0.15               | 0.18                   | Vrms |

| $A_{CR}$                   | Column Pre-emphasis                                       | 2.5V            | Row group=0dB                                                                   | 1                     | 2                  | 3                      | dB   |

| $R_L$                      | DTMF Output Load                                          | 2.5V            | $t_{HD}\!\leq\!\!-23dB$                                                         | 5                     |                    |                        | kΩ   |

| $t_{ m HD}$                | Tone Signal<br>Distortion                                 | 2.5V            | $R_L=5k\Omega$                                                                  |                       | -30                | -23                    | dB   |

| $f_{\rm CLK}$              | Clock Input Rate<br>(Serial Mode)                         |                 |                                                                                 |                       | 100                | 500                    | kHz  |

| t <sub>UP</sub>            | Oscillator Starting<br>Time (When $\overline{CE}$ is low) | 5.0V            | The time from $\overline{CE}$<br>falling edge to normal<br>oscillator operation |                       |                    | 10                     | ms   |

| $f_{OSC}$                  | System Frequency                                          |                 | Crystal=3.5795MHz                                                               | 3.5759                | 3.5795             | 3.5831                 | MHz  |

February 13, 2001

4

## **Functional Description**

The HT9200A/B are DTMF generators for  $\mu$ C interfaces. They are controlled by a  $\mu$ C in the serial mode or the parallel mode (for the HT9200B only).

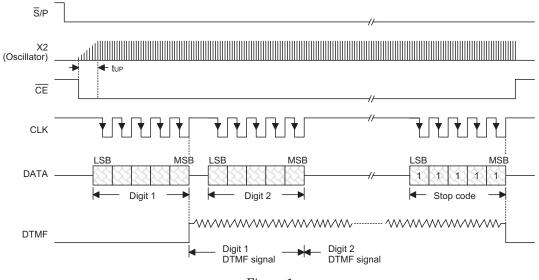

#### Serial mode (HT9200A/B)

The HT9200A/B employ a data input, a 5-bit code, and a synchronous clock to transmit a  $% \left( {{{\rm{A}}_{{\rm{B}}}} \right)$

DTMF signal. Every digit of a phone number to be transmitted is selected by a series of inputs which consist of 5-bit data. Of the 5 bits, the D0(LSB) is the first received bit. The HT9200A/B will latch data on the falling edge of the clock (CLK pin). The relationship between the digital codes and the tone output frequency is shown in Table 1. As for the control timing diagram, refer to Figure 1.

Table 1: Digits vs. input data vs. tone output frequency (serial mode)

| Digit   | <b>D4</b> | D3 | D2 | D1 | DO | <b>Tone Output Frequency (Hz)</b> |

|---------|-----------|----|----|----|----|-----------------------------------|

| 1       | 0         | 0  | 0  | 0  | 1  | 697+1209                          |

| 2       | 0         | 0  | 0  | 1  | 0  | 697+1336                          |

| 3       | 0         | 0  | 0  | 1  | 1  | 697 + 1477                        |

| 4       | 0         | 0  | 1  | 0  | 0  | 770+1209                          |

| 5       | 0         | 0  | 1  | 0  | 1  | 770 + 1336                        |

| 6       | 0         | 0  | 1  | 1  | 0  | 770 + 1477                        |

| 7       | 0         | 0  | 1  | 1  | 1  | 852+1209                          |

| 8       | 0         | 1  | 0  | 0  | 0  | 852+1336                          |

| 9       | 0         | 1  | 0  | 0  | 1  | 852 + 1477                        |

| 0       | 0         | 1  | 0  | 1  | 0  | 941+1336                          |

| *       | 0         | 1  | 0  | 1  | 1  | 941+1209                          |

| #       | 0         | 1  | 1  | 0  | 0  | 941+1477                          |

| А       | 0         | 1  | 1  | 0  | 1  | 697 + 1633                        |

| В       | 0         | 1  | 1  | 1  | 0  | 770 + 1633                        |

| С       | 0         | 1  | 1  | 1  | 1  | 852+1633                          |

| D       | 0         | 0  | 0  | 0  | 0  | 941+1633                          |

|         | 1         | 0  | 0  | 0  | 0  | 697                               |

|         | 1         | 0  | 0  | 0  | 1  | 770                               |

|         | 1         | 0  | 0  | 1  | 0  | 852                               |

| _       | 1         | 0  | 0  | 1  | 1  | 941                               |

|         | 1         | 0  | 1  | 0  | 0  | 1209                              |

|         | 1         | 0  | 1  | 0  | 1  | 1336                              |

|         | 1         | 0  | 1  | 1  | 0  | 1477                              |

|         | 1         | 0  | 1  | 1  | 1  | 1633                              |

| TMF OFF | 1         | 1  | 1  | 1  | 1  | _                                 |

5

Note: The codes not listed in Table 1 are not used D4 is MSB

When the system is operating in the serial mode a pull-high resistor is attached to D0~D3 (for parallel mode) on the input terminal.

For the HT9200B, the  $\overline{S}/P$  pin has to be connected low for serial mode operation.

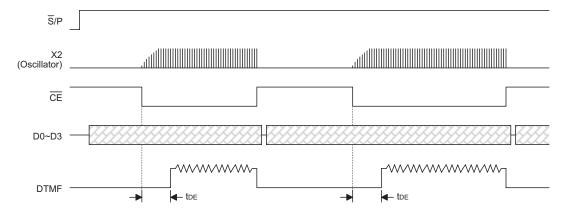

#### Parallel mode (HT9200B)

The HT9200B provides four data inputs D0~D3 to generate their corresponding DTMF signals. The  $\overline{S}/P$  has to be connected high to select the parallel operation mode. Then the input data codes should be determined. Finally, the  $\overline{CE}$  is

connected low to transmit the DTMF signal from the DTMF pin.

The  $T_{DE}$  time (about 6ms) will be delayed from the  $\overline{CE}$  falling edge to the DTMF signal output.

The relationship between the digital codes and the tone output frequency is illustrated in Table 2. As for the control timing diagram, see Figure 2.

When the system is operating in the parallel mode, D0~D3 are all in the floating state. Thus, these data input pins should not float.

Figure 1

| Digit | D3 | D2 | D1 | D0 | Tone Output Frequency (Hz) |

|-------|----|----|----|----|----------------------------|

| 1     | 0  | 0  | 0  | 1  | 697+1209                   |

| 2     | 0  | 0  | 1  | 0  | 697+1336                   |

| 3     | 0  | 0  | 1  | 1  | 697+1477                   |

| 4     | 0  | 1  | 0  | 0  | 770+1209                   |

| 5     | 0  | 1  | 0  | 1  | 770+1336                   |

| 6     | 0  | 1  | 1  | 0  | 770+1477                   |

| 7     | 0  | 1  | 1  | 1  | 852+1209                   |

| 8     | 1  | 0  | 0  | 0  | 852+1336                   |

6

| Table 2: Digits vs. | input data vs. | tone output free | quency (parallel mode) |

|---------------------|----------------|------------------|------------------------|

|                     |                |                  |                        |

| Digit | D3 | D2 | D1 | DO | Tone Output Frequency (Hz) |

|-------|----|----|----|----|----------------------------|

| 9     | 1  | 0  | 0  | 1  | 852+1477                   |

| 0     | 1  | 0  | 1  | 0  | 941+1336                   |

| *     | 1  | 0  | 1  | 1  | 941+1209                   |

| #     | 1  | 1  | 0  | 0  | 941+1477                   |

| А     | 1  | 1  | 0  | 1  | 697+1633                   |

| В     | 1  | 1  | 1  | 0  | 770+1633                   |

| С     | 1  | 1  | 1  | 1  | 852+1633                   |

| D     | 0  | 0  | 0  | 0  | 941+1633                   |

Note: The data (D0~D3) should be ready before the CE becomes low.

Figure 2

| Output Free | <b>Output Frequency (Hz)</b> |          |  |  |  |  |

|-------------|------------------------------|----------|--|--|--|--|

| Specified   | Actual                       | - %Error |  |  |  |  |

| 697         | 699                          | +0.29%   |  |  |  |  |

| 770         | 766                          | 0.52%    |  |  |  |  |

| 852         | 847                          | 0.59%    |  |  |  |  |

| 941         | 948                          | +0.74%   |  |  |  |  |

| 1209        | 1215                         | +0.50%   |  |  |  |  |

| 1336        | 1332                         | 0.30%    |  |  |  |  |

| 1477        | 1472                         | 0.34%    |  |  |  |  |

Tone frequency

% Error does not contain the crystal frequency drift

February 13, 2001

7

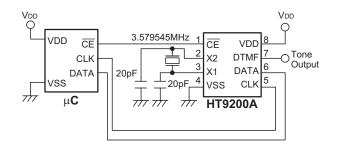

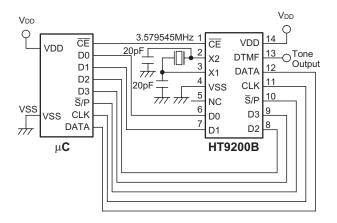

# **Application Circuits**

Serial mode

Serial/parallel mode

8

Holtek Semiconductor Inc. (Headquarters) No.3 Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan, R.O.C. Tel: 886-3-563-1999 Fax: 886-3-563-1189

Holtek Semiconductor Inc. (Taipei Office) 11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan, R.O.C. Tel: 886-2-2782-9635 Fax: 886-2-2782-9636 Fax: 886-2-2782-7128 (International sales hotline)

Holtek Semiconductor (Hong Kong) Ltd. RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong Tel: 852-2-745-8288 Fax: 852-2-742-8657

Holmate Technology Corp. 48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539 Tel: 510-252-9880 Fax: 510-252-9885

Copyright  $\odot$  2001 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

9